#### **OVERVIEW**

The SM5073 series are VCXO ICs with built-in varicap diode. They use a recently developed negative-resistance switching oscillation circuit, at oscillation startup and during normal oscillation, for both good oscillation startup characteristics and wide pullrange. Furthermore, it employs a CMOS process varicap diode, and also features all the necessary VCXO structure circuit components on a single chip, forming a VCXO with just the connection of an external crystal.

#### **FEATURES**

- 3.0 to 3.6V supply voltage range

- 10MHz to 60MHz operating frequency (varies with version)

- Uses negative-resistance switching function

- Varicap diode built-in

- Frequency divider built-in (varies with version:  $f_O$ ,  $f_O/2$ ,  $f_O/4$ ,  $f_O/8$ ,  $f_O/16$ ,  $f_O/32$ )

- CMOS output level

- $50 \pm 10\%$  output duty

- 6mA (min) output drive capability

- 15pF output load capacitance C<sub>L</sub>

- Standby function

High impedance in standby mode (oscillator continues running)

- Package: 8-pin SOP (SM5073××S)

## **APPLICATIONS**

- VCXO modules

- Communications application

- Networking application

- Broadcasting application

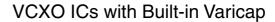

### PACKAGE DIMENSIONS

(Unit: mm)

#### **SERIES LINEUP**

| Version Typical oscillatio |                              | Output frequency |                        |                        |                        |                        |                        |  |  |

|----------------------------|------------------------------|------------------|------------------------|------------------------|------------------------|------------------------|------------------------|--|--|

| Version                    | frequency <sup>1</sup> [MHz] | SM5073×1S        | SM5073×2S <sup>2</sup> | SM5073×3S <sup>2</sup> | SM5073×4S <sup>2</sup> | SM5073×5S <sup>2</sup> | SM5073×6S <sup>2</sup> |  |  |

| SM5073A×S                  | 16                           |                  |                        |                        |                        |                        |                        |  |  |

| SM5073B×S                  | 23                           |                  |                        |                        |                        |                        | £ /00                  |  |  |

| SM5073C×S                  | 30                           | f f              | £ /O                   | £ /A                   | 4 /0                   | 1 40                   |                        |  |  |

| SM5073D×S                  | 37                           | t <sub>o</sub>   | f <sub>O</sub> /2      | f <sub>O</sub> /4      | f <sub>O</sub> /8      | f <sub>O</sub> /16     | f <sub>O</sub> /32     |  |  |

| SM5073E×S                  | 44                           |                  |                        |                        |                        |                        |                        |  |  |

| SM5073F×S                  | 51                           |                  |                        |                        |                        |                        |                        |  |  |

The typical oscillation frequency is the oscillation frequency criteria for use when selecting the device version. Note that the oscillation characteristics and pullability vary with the crystal used and the mounting conditions. Even for the same frequency, the optimal version can vary with crystal characteristics, so careful evaluation should be exercised when selecting the device version.

#### ORDERING INFORMATION

| Device    | Package   |

|-----------|-----------|

| SM5073××S | 8-pin SOP |

<sup>2.</sup> These versions are produced after receiving a purchase order. Please ask our Sales & Marketing section for further detail.

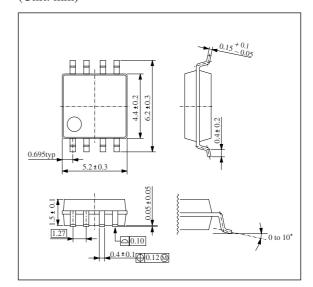

# **PINOUT**

(Top view)

# **PIN DESCRIPTION**

| Number | Name | I/O | Description                                     | Function                                                                                                                                                                   |

|--------|------|-----|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | XTN  | 0   | Amplifier output pin                            | Crystal connection pins. Crystal is connected between XT and XTN.                                                                                                          |

| 2      | VC   | I   | Oscillation frequency control voltage input pin | Positive polarity (frequency increases with increasing voltage)                                                                                                            |

| 3      | INHN | I   | Output state control voltage input pin          | High-impedance output when LOW, pull-up resistor built-in                                                                                                                  |

| 4      | VSS  | -   | (–) supply pin                                  |                                                                                                                                                                            |

| 5      | Q    | 0   | Output pin                                      | Output frequency determined by internal circuit to one of f <sub>O</sub> , f <sub>O</sub> /2, f <sub>O</sub> /4, f <sub>O</sub> /8, f <sub>O</sub> /16, f <sub>O</sub> /32 |

| 6      | NC   | -   | No connection                                   |                                                                                                                                                                            |

| 7      | VDD  | -   | (+) supply pin                                  |                                                                                                                                                                            |

| 8      | XT   | I   | Amplifier input pin                             | Crystal connection pins. Crystal is connected between XT and XTN.                                                                                                          |

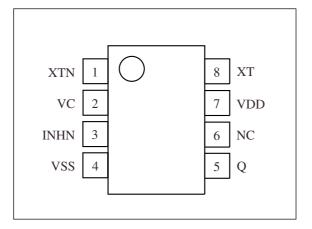

# **BLOCK DIAGRAM**

Note. ESD of XT pin is inferior to other pins.

ESD of all pins excluding XT pin is equivalent to that of our other oscillator products.

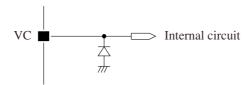

VC pin has no protection circuit at V<sub>DD</sub> side. (See figure below.)

## **ABSOLUTE MAXIMUM RATINGS**

$V_{SS} = 0V$  unless otherwise noted.

| Parameter                   | Symbol           | Conditions                      | Rating                                     | Unit |

|-----------------------------|------------------|---------------------------------|--------------------------------------------|------|

| Supply voltage range        | V <sub>DD</sub>  |                                 | -0.5 to 7.0                                | V    |

| Input voltage range         | V                | All input pins excluding VC pin | -0.5 to V <sub>DD</sub> + 0.5              | V    |

| input voitage range         | V <sub>IN</sub>  | VC pin                          | -0.5 to V <sub>DD</sub> + 2.5 <sup>1</sup> | V    |

| Output voltage range        | V <sub>OUT</sub> |                                 | -0.5 to V <sub>DD</sub> + 0.5              | V    |

| Operating temperature range | T <sub>opr</sub> |                                 | -40 to +85                                 | °C   |

| Storage temperature range   | T <sub>STG</sub> |                                 | -55 to +125                                | °C   |

| Output current              | l <sub>out</sub> |                                 | 20                                         | mA   |

| Power dissipation           | P <sub>D</sub>   |                                 | 500                                        | mW   |

<sup>1.</sup> It should not exceed + 7.0V.

## **RECOMMENDED OPERATING CONDITIONS**

$V_{SS}$  = 0V, f = 10MHz to 60MHz,  $C_L \leq$  15pF unless otherwise noted.

| Parameter                | Symbol           | Conditions |                 | Rating |                 | Unit |

|--------------------------|------------------|------------|-----------------|--------|-----------------|------|

|                          | Syllibol         | Conditions | Min             | Тур    | Max             | V V  |

| Operating supply voltage | V <sub>DD</sub>  |            | 3.0             | -      | 3.6             | V    |

| Input voltage            | V <sub>IN</sub>  |            | V <sub>SS</sub> | -      | V <sub>DD</sub> | V    |

| Operating temperature    | T <sub>OPR</sub> |            | -40             | -      | +85             | °C   |

# **ELECTRICAL CHARACTERISTICS**

# SM5073A×S

$V_{DD}$  = 3.0 to 3.6V,  $V_{C}$  = 1.65V,  $V_{SS}$  = 0V, Ta = -40 to +85°C, unless otherwise noted.

| Davamatan                 | Comple et       | O a a diki a a                                      |                                          |                    | Rating |                    | 11   |

|---------------------------|-----------------|-----------------------------------------------------|------------------------------------------|--------------------|--------|--------------------|------|

| Parameter                 | Symbol          | Condition                                           | IS                                       | Min                | Тур    | Max                | Unit |

| HIGH-level output voltage | V <sub>OH</sub> | Q: Measurement circuit 1, I <sub>OH</sub>           | Q: Measurement circuit 1, $I_{OH} = 6mA$ |                    | 2.75   | -                  | ٧    |

| LOW-level output voltage  | V <sub>OL</sub> | Q: Measurement circuit 1, I <sub>OL</sub>           | _ = 6mA                                  | -                  | 0.2    | 0.4                | ٧    |

| Output lookage gurrent    |                 | Q: Measurement circuit 6,                           | $V_{OH} = V_{DD}$                        | -                  | -      | 10                 | μΑ   |

| Output leakage current    | I <sub>Z</sub>  | INHN = LOW                                          | V <sub>OL</sub> = V <sub>SS</sub>        | -                  | -      | 10                 | μA   |

| HIGH-level input voltage  | V <sub>IH</sub> | INHN                                                |                                          | 0.7V <sub>DD</sub> | -      | -                  | ٧    |

| LOW-level input voltage   | V <sub>IL</sub> | INHN                                                |                                          | -                  | -      | 0.3V <sub>DD</sub> | ٧    |

|                           |                 |                                                     | SM5073A1S                                | -                  | 8      | 23                 | mA   |

| Current concumption       |                 | Measurement circuit 2, load circuit 1, INHN = open, | SM5073A2S                                | -                  | 7.5    | 22.5               | mA   |

| Current consumption       | I <sub>DD</sub> | C <sub>L</sub> = 15pF,<br>f = 16MHz                 | SM5073A3S                                | -                  | 7      | 22                 | mA   |

|                           |                 | T = TOWN IZ                                         | SM5073A4S to 6S                          | -                  | 7      | 22                 | mA   |

| INHN pull-up resistance   | R <sub>UP</sub> | Measurement circuit 3                               | Measurement circuit 3                    |                    | 100    | 180                | kΩ   |

|                           | R <sub>f</sub>  | Design value. A monitor pattern on a wafer is       |                                          | 150                | 300    | 540                | kΩ   |

|                           | R <sub>D</sub>  | tested.                                             |                                          | 0.67               | 0.96   | 1.25               | kΩ   |

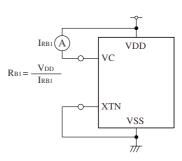

| Built-in resistance       | R <sub>B1</sub> | Measurement circuit 4                               |                                          | 100                | 200    | 360                | kΩ   |

|                           | R <sub>B2</sub> | Design value. A monitor patte tested.               | rn on a wafer is                         | 50                 | 100    | 180                | kΩ   |

|                           | 0               | Design value. A monitor                             | V <sub>C</sub> = 0.3V                    | 11.0               | 14.4   | 17.8               | pF   |

|                           | C <sub>V</sub>  | pattern on a wafer is tested.                       | V <sub>C</sub> = 3.0V                    | 2.4                | 4.0    | 5.6                | pF   |

| Built-in capacitance      | C <sub>G</sub>  |                                                     | •                                        | 25.5               | 30     | 34.5               | pF   |

|                           | C <sub>D</sub>  | Design value. A monitor patte tested.               | rn on a wafer is                         | 34                 | 40     | 46                 | pF   |

|                           | C <sub>C</sub>  |                                                     |                                          | 8.5                | 10     | 11.5               | pF   |

# SM5073B×S

$V_{\rm DD}$  = 3.0 to 3.6V,  $V_{\rm C}$  = 1.65V,  $V_{\rm SS}$  = 0V, Ta = -40 to +85°C, unless otherwise noted.

| Parameter                 | Combal          | Conditions                                                                           |                                                 |                    | Rating |                    | Unit |

|---------------------------|-----------------|--------------------------------------------------------------------------------------|-------------------------------------------------|--------------------|--------|--------------------|------|

| Parameter                 | Symbol          | Condition                                                                            | is                                              | Min                | Тур    | Тур Мах            |      |

| HIGH-level output voltage | V <sub>OH</sub> | Q: Measurement circuit 1, I <sub>OI</sub>                                            | Q: Measurement circuit 1, I <sub>OH</sub> = 6mA |                    | 2.75   | -                  | ٧    |

| LOW-level output voltage  | V <sub>OL</sub> | Q: Measurement circuit 1, I <sub>OL</sub>                                            | = 6mA                                           | -                  | 0.2    | 0.4                | V    |

| Output leakage current    | 1               | Q: Measurement circuit 6, V <sub>OH</sub> = V <sub>DD</sub>                          |                                                 | -                  | -      | 10                 | μA   |

| Output leakage current    | I <sub>Z</sub>  | INHN = LOW                                                                           | $V_{OL} = V_{SS}$                               | _                  | -      | 10                 | μA   |

| HIGH-level input voltage  | V <sub>IH</sub> | INHN                                                                                 | •                                               | 0.7V <sub>DD</sub> | -      | -                  | ٧    |

| LOW-level input voltage   | V <sub>IL</sub> | INHN                                                                                 |                                                 | -                  | -      | 0.3V <sub>DD</sub> | ٧    |

|                           |                 |                                                                                      | SM5073B1S                                       | -                  | 9      | 25                 | mA   |

| Current concumption       |                 | Measurement circuit 2, load circuit 1, INHN = open, C <sub>L</sub> = 15pF, f = 23MHz | SM5073B2S                                       | _                  | 8      | 24                 | mA   |

| Current consumption       | l <sub>DD</sub> |                                                                                      | SM5073B3S                                       | -                  | 7.5    | 23.5               | mA   |

|                           |                 |                                                                                      | SM5073B4S to 6S                                 | -                  | 7.5    | 23.5               | mA   |

| INHN pull-up resistance   | R <sub>UP</sub> | Measurement circuit 3                                                                | Measurement circuit 3                           |                    | 100    | 180                | kΩ   |

|                           | R <sub>f</sub>  | Design value. A monitor pattern on a wafer is                                        |                                                 | 150                | 300    | 540                | kΩ   |

|                           | R <sub>D</sub>  | tested.                                                                              |                                                 | 0.50               | 0.72   | 0.94               | kΩ   |

| Built-in resistance       | R <sub>B1</sub> | Measurement circuit 4                                                                |                                                 | 100                | 200    | 360                | kΩ   |

|                           | R <sub>B2</sub> | Design value. A monitor patte tested.                                                | rn on a wafer is                                | 50                 | 100    | 180                | kΩ   |

|                           |                 | Design value. A monitor                                                              | V <sub>C</sub> = 0.3V                           | 11.0               | 14.6   | 18.2               | pF   |

|                           | C <sub>V</sub>  | pattern on a wafer is tested.                                                        | V <sub>C</sub> = 3.0V                           | 2.3                | 4.0    | 5.7                | pF   |

| Built-in capacitance      | C <sub>G</sub>  |                                                                                      | •                                               | 25.5               | 30     | 34.5               | pF   |

|                           | C <sub>D</sub>  | Design value. A monitor patte tested.                                                | rn on a wafer is                                | 34                 | 40     | 46                 | pF   |

|                           | C <sub>C</sub>  |                                                                                      |                                                 | 12.7               | 15     | 17.3               | pF   |

SM5073C×S

$V_{DD}$  = 3.0 to 3.6V,  $V_{C}$  = 1.65V,  $V_{SS}$  = 0V, Ta = -40 to +85°C, unless otherwise noted.

| Davamatav                 | Combal          | Conditions                                            |                       |                    |      | 1124               |      |

|---------------------------|-----------------|-------------------------------------------------------|-----------------------|--------------------|------|--------------------|------|

| Parameter                 | Symbol          | Condition                                             | IS                    | Min                | Тур  | Max                | Unit |

| HIGH-level output voltage | V <sub>OH</sub> | Q: Measurement circuit 1, I <sub>OH</sub>             | <sub>I</sub> = 6mA    | 2.5                | 2.75 | -                  | V    |

| LOW-level output voltage  | V <sub>OL</sub> | Q: Measurement circuit 1, I <sub>OL</sub>             | = 6mA                 | -                  | 0.2  | 0.4                | ٧    |

| Output leakage current    |                 | Q: Measurement circuit 6,                             | $V_{OH} = V_{DD}$     | -                  | -    | 10                 | μA   |

| Output leakage current    | I <sub>Z</sub>  | INHN = LOW                                            | $V_{OL} = V_{SS}$     | -                  | -    | 10                 | μA   |

| HIGH-level input voltage  | V <sub>IH</sub> | INHN                                                  |                       | 0.7V <sub>DD</sub> | -    | -                  | V    |

| LOW-level input voltage   | V <sub>IL</sub> | INHN                                                  |                       | -                  | -    | 0.3V <sub>DD</sub> | V    |

|                           |                 |                                                       | SM5073C1S             | -                  | 10   | 28                 | mA   |

| Current consumption       |                 | Measurement circuit 2, load circuit 1, INHN = open,   | SM5073C2S             | -                  | 9    | 27                 | mA   |

|                           | I <sub>DD</sub> | C <sub>L</sub> = 15pF,<br>f = 30MHz                   | SM5073C3S             | -                  | 8.5  | 26.5               | mA   |

|                           |                 |                                                       | SM5073C4S to 6S       | -                  | 8    | 26                 | mA   |

| INHN pull-up resistance   | R <sub>UP</sub> | Measurement circuit 3                                 |                       | 50                 | 100  | 180                | kΩ   |

|                           | R <sub>f</sub>  | Design value. A monitor pattern on a wafer is         |                       | 150                | 300  | 540                | kΩ   |

|                           | R <sub>D</sub>  | tested.                                               |                       | 0.50               | 0.72 | 0.94               | kΩ   |

| Built-in resistance       | R <sub>B1</sub> | Measurement circuit 4                                 |                       | 100                | 200  | 360                | kΩ   |

|                           | R <sub>B2</sub> | Design value. A monitor pattern on a wafer is tested. |                       | 50                 | 100  | 180                | kΩ   |

|                           |                 | Design value. A monitor                               | V <sub>C</sub> = 0.3V | 11.0               | 14.6 | 18.2               | pF   |

|                           | C <sub>V</sub>  | pattern on a wafer is tested.                         | V <sub>C</sub> = 3.0V | 2.3                | 4.0  | 5.7                | pF   |

| Built-in capacitance      | C <sub>G</sub>  |                                                       | •                     | 25.5               | 30   | 34.5               | pF   |

|                           | C <sub>D</sub>  | Design value. A monitor pattern on a wafer is tested. |                       | 25.5               | 30   | 34.5               | pF   |

|                           | C <sub>C</sub>  |                                                       |                       | 29.7               | 35   | 40.3               | pF   |

# SM5073D×S

$V_{\rm DD}$  = 3.0 to 3.6V,  $V_{\rm C}$  = 1.65V,  $V_{\rm SS}$  = 0V, Ta = -40 to +85°C, unless otherwise noted.

| Parameter                 | Combal          | Conditions                                                  |                                                 |                    | Rating |                    | Unit |

|---------------------------|-----------------|-------------------------------------------------------------|-------------------------------------------------|--------------------|--------|--------------------|------|

| Parameter                 | Symbol          | Condition                                                   | IS                                              | Min                | Тур    | Тур Мах            |      |

| HIGH-level output voltage | V <sub>OH</sub> | Q: Measurement circuit 1, I <sub>OH</sub>                   | Q: Measurement circuit 1, I <sub>OH</sub> = 6mA |                    | 2.75   | -                  | V    |

| LOW-level output voltage  | V <sub>OL</sub> | Q: Measurement circuit 1, I <sub>OL</sub>                   | = 6mA                                           | -                  | 0.2    | 0.4                | V    |

| Output leakage current    |                 | Q: Measurement circuit 6, V <sub>OH</sub> = V <sub>DD</sub> |                                                 | -                  | -      | 10                 | μА   |

| Output leakage current    | I <sub>Z</sub>  | INHN = LOW                                                  | V <sub>OL</sub> = V <sub>SS</sub>               | -                  | -      | 10                 | μА   |

| HIGH-level input voltage  | V <sub>IH</sub> | INHN                                                        | •                                               | 0.7V <sub>DD</sub> | -      | -                  | V    |

| LOW-level input voltage   | V <sub>IL</sub> | INHN                                                        |                                                 | -                  | -      | 0.3V <sub>DD</sub> | V    |

|                           |                 |                                                             | SM5073D1S                                       | -                  | 11     | 30                 | mA   |

| Current concumption       |                 | Measurement circuit 2, load circuit 1, INHN = open,         | SM5073D2S                                       | -                  | 9.5    | 28.5               | mA   |

| Current consumption       | I <sub>DD</sub> | C <sub>L</sub> = 15pF,<br>f = 37MHz                         | SM5073D3S                                       | -                  | 9      | 28                 | mA   |

|                           |                 |                                                             | SM5073D4S to 6S                                 | -                  | 8.5    | 27.5               | mA   |

| INHN pull-up resistance   | R <sub>UP</sub> | Measurement circuit 3                                       |                                                 | 50                 | 100    | 180                | kΩ   |

|                           | R <sub>f</sub>  | Design value. A monitor pattern on a wafer is               |                                                 | 150                | 300    | 540                | kΩ   |

|                           | R <sub>D</sub>  | tested.                                                     |                                                 | 0.25               | 0.36   | 0.47               | kΩ   |

| Built-in resistance       | R <sub>B1</sub> | Measurement circuit 4                                       |                                                 | 100                | 200    | 360                | kΩ   |

|                           | R <sub>B2</sub> | Design value. A monitor patte tested.                       | rn on a wafer is                                | 50                 | 100    | 180                | kΩ   |

|                           |                 | Design value. A monitor                                     | V <sub>C</sub> = 0.3V                           | 11.0               | 14.6   | 18.2               | pF   |

|                           | C <sub>V</sub>  | pattern on a wafer is tested.                               | V <sub>C</sub> = 3.0V                           | 2.3                | 4.0    | 5.7                | pF   |

| Built-in capacitance      | C <sub>G</sub>  |                                                             | •                                               | 25.5               | 30     | 34.5               | pF   |

|                           | C <sub>D</sub>  | Design value. A monitor patte tested.                       | rn on a wafer is                                | 25.5               | 30     | 34.5               | pF   |

|                           | C <sub>C</sub>  |                                                             |                                                 | 34                 | 40     | 46                 | pF   |

SM5073E×S

$V_{\rm DD}$  = 3.0 to 3.6V,  $V_{\rm C}$  = 1.65V,  $V_{\rm SS}$  = 0V, Ta = -40 to +85°C, unless otherwise noted.

| Parameter                 | Combal          | Conditions                                                  |                       |                    | Rating |                    | Unit  |

|---------------------------|-----------------|-------------------------------------------------------------|-----------------------|--------------------|--------|--------------------|-------|

| Parameter                 | Symbol          | Condition                                                   | is                    | Min                | Тур    | Max                | Offic |

| HIGH-level output voltage | V <sub>OH</sub> | Q: Measurement circuit 1, I <sub>OH</sub> = 6mA             |                       | 2.5                | 2.75   | -                  | V     |

| LOW-level output voltage  | V <sub>OL</sub> | Q: Measurement circuit 1, I <sub>OL</sub>                   | = 6mA                 | -                  | 0.2    | 0.4                | V     |

| Output leakage current    | 1               | Q: Measurement circuit 6, V <sub>OH</sub> = V <sub>DD</sub> |                       | -                  | -      | 10                 | μA    |

| Output leakage current    | I <sub>Z</sub>  | INHN = LOW                                                  | $V_{OL} = V_{SS}$     | _                  | -      | 10                 | μA    |

| HIGH-level input voltage  | V <sub>IH</sub> | INHN                                                        | •                     | 0.7V <sub>DD</sub> | -      | -                  | ٧     |

| LOW-level input voltage   | V <sub>IL</sub> | INHN                                                        |                       | -                  | -      | 0.3V <sub>DD</sub> | ٧     |

|                           |                 |                                                             | SM5073E1S             | -                  | 12     | 32                 | mA    |

| Current concumption       |                 | Measurement circuit 2, load circuit 1, INHN = open,         | SM5073E2S             | _                  | 10.5   | 30.5               | mA    |

| Current consumption       | l <sub>DD</sub> | C <sub>L</sub> = 15pF,<br>f = 44MHz                         | SM5073E3S             | -                  | 9.5    | 29.5               | mA    |

|                           |                 |                                                             | SM5073E4S to 6S       | -                  | 9      | 29                 | mA    |

| INHN pull-up resistance   | R <sub>UP</sub> | Measurement circuit 3                                       |                       | 50                 | 100    | 180                | kΩ    |

|                           | R <sub>f</sub>  | Design value. A monitor pattern on a wafer is               |                       | 150                | 300    | 540                | kΩ    |

|                           | R <sub>D</sub>  | tested.                                                     |                       | 0.25               | 0.36   | 0.47               | kΩ    |

| Built-in resistance       | R <sub>B1</sub> | Measurement circuit 4                                       |                       | 100                | 200    | 360                | kΩ    |

|                           | R <sub>B2</sub> | Design value. A monitor patte tested.                       | rn on a wafer is      | 50                 | 100    | 180                | kΩ    |

|                           |                 | Design value. A monitor                                     | V <sub>C</sub> = 0.3V | 11.0               | 14.6   | 18.2               | pF    |

|                           | C <sub>V</sub>  | pattern on a wafer is tested.                               | V <sub>C</sub> = 3.0V | 2.3                | 4.0    | 5.7                | pF    |

| Built-in capacitance      | C <sub>G</sub>  |                                                             | •                     | 21.2               | 25     | 28.8               | pF    |

|                           | C <sub>D</sub>  | Design value. A monitor patte tested.                       | rn on a wafer is      | 21.2               | 25     | 28.8               | pF    |

|                           | C <sub>C</sub>  |                                                             |                       | 42.5               | 50     | 57.5               | pF    |

SM5073F×S

$V_{DD}$  = 3.0 to 3.6V,  $V_{C}$  = 1.65V,  $V_{SS}$  = 0V, Ta = -40 to +85°C, unless otherwise noted.

| Davamatav                 | Combal          | Conditions                                                                           |                                                       |                    | Unit |                    |    |

|---------------------------|-----------------|--------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------|------|--------------------|----|

| Parameter                 | Symbol          | Condition                                                                            | IS                                                    | Min                | Тур  | Тур Мах            |    |

| HIGH-level output voltage | V <sub>OH</sub> | Q: Measurement circuit 1, I <sub>OH</sub>                                            | Q: Measurement circuit 1, I <sub>OH</sub> = 6mA       |                    | 2.75 | -                  | ٧  |

| LOW-level output voltage  | V <sub>OL</sub> | Q: Measurement circuit 1, I <sub>OL</sub>                                            | = 6mA                                                 | -                  | 0.2  | 0.4                | ٧  |

| Output leakage current    |                 | Q: Measurement circuit 6,                                                            | $V_{OH} = V_{DD}$                                     | -                  | -    | 10                 | μA |

| Output leakage current    | I <sub>Z</sub>  | INHN = LOW                                                                           | V <sub>OL</sub> = V <sub>SS</sub>                     | -                  | -    | 10                 | μA |

| HIGH-level input voltage  | V <sub>IH</sub> | INHN                                                                                 |                                                       | 0.7V <sub>DD</sub> | -    | -                  | V  |

| LOW-level input voltage   | V <sub>IL</sub> | INHN                                                                                 |                                                       | -                  | -    | 0.3V <sub>DD</sub> | ٧  |

|                           |                 |                                                                                      | SM5073F1S                                             | -                  | 13   | 35                 | mA |

| Current consumption       |                 | Measurement circuit 2, load circuit 1, INHN = open, C <sub>L</sub> = 15pF, f = 51MHz | SM5073F2S                                             | -                  | 11   | 33                 | mA |

|                           | I <sub>DD</sub> |                                                                                      | SM5073F3S                                             | -                  | 10   | 32                 | mA |

|                           |                 |                                                                                      | SM5073F4S to 6S                                       | -                  | 9.5  | 31.5               | mA |

| INHN pull-up resistance   | R <sub>UP</sub> | Measurement circuit 3                                                                |                                                       | 50                 | 100  | 180                | kΩ |

|                           | R <sub>f</sub>  | Design value. A monitor pattern on a wafer is                                        |                                                       | 150                | 300  | 540                | kΩ |

|                           | R <sub>D</sub>  | tested.                                                                              |                                                       | 0.25               | 0.36 | 0.47               | kΩ |

| Built-in resistance       | R <sub>B1</sub> | Measurement circuit 4                                                                |                                                       | 100                | 200  | 360                | kΩ |

|                           | R <sub>B2</sub> | Design value. A monitor patte tested.                                                | Design value. A monitor pattern on a wafer is tested. |                    | 100  | 180                | kΩ |

|                           |                 | Design value. A monitor                                                              | V <sub>C</sub> = 0.3V                                 | 9.5                | 12.5 | 15.5               | pF |

|                           | C <sub>V</sub>  | pattern on a wafer is tested.                                                        | V <sub>C</sub> = 3.0V                                 | 2.0                | 3.5  | 5.0                | pF |

| Built-in capacitance      | C <sub>G</sub>  |                                                                                      | •                                                     | 17                 | 20   | 23                 | pF |

|                           | C <sub>D</sub>  | Design value. A monitor pattern on a wafer is tested.                                |                                                       | 17                 | 20   | 23                 | pF |

|                           | C <sub>C</sub>  |                                                                                      |                                                       | 42.5               | 50   | 57.5               | pF |

#### **SWITCHING CHARACTERISTICS**

$V_{DD}$  = 3.0 to 3.6V,  $V_{C}$  = 1.65V,  $V_{SS}$  = 0V, Ta = -40 to +85°C, unless otherwise noted

| Parameter                 | Cumbal           | Conditions                                                                                      | Rating <sup>1</sup> |     |     | Unit |  |

|---------------------------|------------------|-------------------------------------------------------------------------------------------------|---------------------|-----|-----|------|--|

| Parameter                 | Symbol           | Conditions                                                                                      | Min                 | Тур | Max | Unit |  |

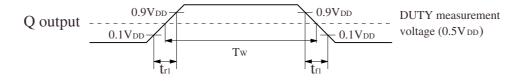

| Output rise time          | t <sub>r1</sub>  |                                                                                                 | -                   | 2.5 | 6   | ns   |  |

| Output fall time          | t <sub>f1</sub>  |                                                                                                 | -                   | 2.5 | 6   | ns   |  |

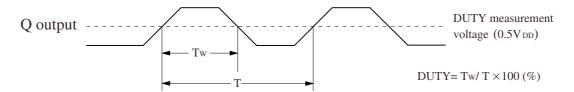

| Output duty cycle         | Duty             | Measurement circuit 2, load circuit 1, V <sub>DD</sub> = 3.3V, Ta = 25°C, C <sub>L</sub> = 15pF | 40                  | 50  | 60  | %    |  |

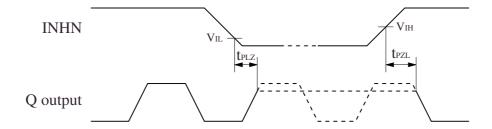

| Output disable delay time | t <sub>PLZ</sub> | Measurement circuit 5, load circuit 1,                                                          | -                   | -   | 100 | ns   |  |

| Output enable delay time  | t <sub>PZL</sub> | $V_{DD} = 3.3V$ , Ta = 25°C, $C_L \le 15pF$                                                     | _                   | _   | 100 | ns   |  |

<sup>1.</sup> The switching characteristics apply for normal output waveforms. Note that, depending on the matching of the SM5073 series version and crystal, normal waveform output may not be continuous.

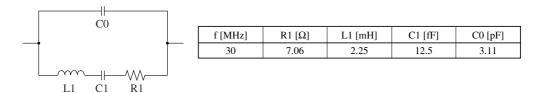

# Current consumption and Output waveform with NPC's standard crystal

### **FUNCTIONAL DESCRIPTION**

## **Standby Function**

When INHN goes LOW, the Q output pin becomes high impedance.

| INHN           | Q                                                                | Oscillator |

|----------------|------------------------------------------------------------------|------------|

| HIGH (or open) | Any $f_O$ , $f_O/2$ , $f_O/4$ , $f_O/8$ , $f_O/16$ , or $f_O/32$ | Operating  |

| LOW            | High impedance                                                   | Operating  |

### **MEASUREMENT CIRCUITS**

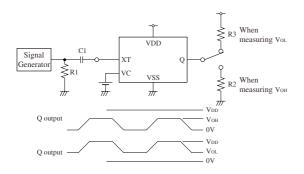

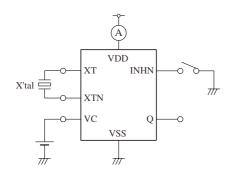

### **Measurement Circuit 1**

XT input signal: 2.5Vp-p, 10MHz, sine wave C1 = 0.001 $\mu$ F, R1 = 50 $\Omega$ , R2 = 417 $\Omega$ , R3 = 434 $\Omega$ , V<sub>C</sub> = 1.65V

### **Measurement Circuit 4**

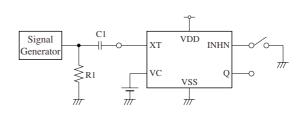

### **Measurement Circuit 2**

$V_C = 1.65V$ , INHN = open, crystal oscillation

### **Measurement Circuit 5**

XT input signal: 2.5Vp-p, 10MHz, sine wave C1 = 0.001  $\mu F,$  R1 =  $50\Omega,$   $V_C$  = 1.65V

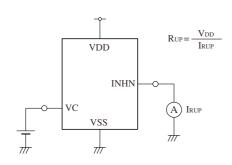

### **Measurement Circuit 3**

$V_{\rm C} = 1.65 V$

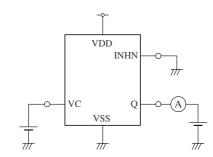

### **Measurement Circuit 6**

$$V_{\rm C} = 1.65 V$$

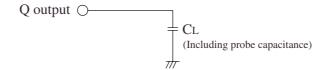

## **Load Circuit 1**

## **Switching Time Measurement Waveform**

## Output duty level, t<sub>r</sub>, t<sub>f</sub>

## **Output duty cycle**

# **Output Enable/Disable Delay Times**

INHN input waveform  $tr = tf \le 10$ ns

Please pay your attention to the following points at time of using the products shown in this document.

The products shown in this document (hereinafter "Products") are not intended to be used for the apparatus that exerts harmful influence on human lives due to the defects, failure or malfunction of the Products. Customers are requested to obtain prior written agreement for such use from SEIKO NPC CORPORATION (hereinafter "NPC"). Customers shall be solely responsible for, and indemnify and hold NPC free and harmless from, any and all claims, damages, losses, expenses or lawsuits, due to such use without such agreement. NPC reserves the right to change the specifications of the Products in order to improve the characteristic or reliability thereof. NPC makes no claim or warranty that the contents described in this document dose not infringe any intellectual property right or other similar right owned by third parties. Therefore, NPC shall not be responsible for such problems, even if the use is in accordance with the descriptions provided in this document. Any descriptions including applications, circuits, and the parameters of the Products in this document are for reference to use the Products, and shall not be guaranteed free from defect, inapplicability to the design for the mass-production products without further testing or modification. Customers are requested not to export or re-export, directly or indirectly, the Products to any country or any entity not in compliance with or in violation of the national export administration laws, treaties, orders and regulations. Customers are requested appropriately take steps to obtain required permissions or approvals from appropriate government agencies.

#### SEIKO NPC CORPORATION

15-6, Nihombashi-kabutocho, Chuo-ku, Tokyo 103-0026, Japan Telephone: +81-3-6667-6601 Facsimile: +81-3-6667-6611 http://www.npc.co.jp/ Email: sales@npc.co.jp

NC0213BE 2006.04